لینک ها

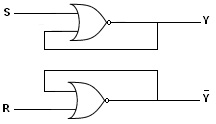

فلیپ فلاپ SR

|

|

|

فلیپ فلاپ SR یک المان فیزیکی است که می تواند به عنوان یک عنصر تاخیر دهنده به کار گرفته شود. این المان فیزیکی دارای دو ورودی به نام های R و S می باشد و دو خروجی دارد که یکی متمم دیگری است.

طرز کاراین فلیپ فلاپ در جدول صحت به این شکل است که وقتی عملکرد مدار را بررسی می کنیم اگر S=1 و R=0 باشد، اصطلاحا می گویند مدار set است یعنی خروجی آن 1 شده است. اگر پس از آن S=0 شود، مدار در وضعیت set باقی می ماند ولی اگر R=1 شود اصطلاحا می گویند مدار Reset شده است یعنی خروجی در این لحظه صفر است، و اگر در این لحظه R=0 شود مدار در حالت Reset باقی می ماند. بنابراین R=0 و S=0 در خروجی نشان می دهد که کدامیک از S یا R آخرین بار برابر 1 بوده است. یعنی مدار آخرین وضعیت غیر صفر ورودی را به خاطر سپرده است. مطابق جدول کارنو اگر R و S همزمان در حالت 1 قرار گیرند مدار در حالت نامشخص خواهد بود. به این خاطر مدارهای دارای فلیپ فلاپ SR را طوری طراحی می کنند که هیچ گاه ورودی های S و R همزمان برابر 1 نشود.

این مورد محدودیتی برای فلیپ فلاپ SR است، که در فلیپ فلاپ JK این نقص برطرف شده است.

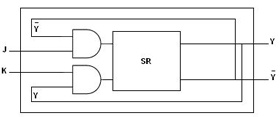

فلیپ فلاپ JK

این عنصر تاخیر دهنده دارای دو ورودی به نام J و K می باشد و دو خروجی آن یکی متمم دیگری است و در آن محدودیت فلیپ فلاپ SR را رفع کرده اند و دو ورودی J=1 و 1=K برای این مدار قابل قبول است.

در این فلیپ فلاپ همانند نوع SR ورودی تمام صفر یعنی J=0 و K=0 تاثیری در حالت خروجی فلیپ فلاپ ندارد و همان حالت قبلی حفظ می شود. ولی اگر J=1 و 1=K باشد یک ورودی قابل قبول است که باعث تغییر حالت در مقدار خروجی می شود.

|

|

|

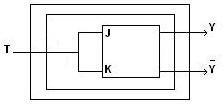

فلیپ فلاپ T

|

|

|

این عنصر تاخیر دهنده دارای یک ورودی به نام T است و دو خروجی به صورت Y و متمم آن دارد.

چنانچه T=1 شود باعث تغییر در خروجی می شود یعنی اگر خروجی صفر باشد مقدار آن یک می شود و برعکس اگر خروجی یک باشد مقدار آن صفر می شود. این فلیپ فلاپ را به این خاطر فلیپ فلاپ جهشی نیز می نامند.

فلیپ فلاپ T همانند فلیپ فلاپ JK است که دو ورودی آن از یک متغیر مقدار می گیرد یعنی یا هر دو J و K مقدار صفر و یا هر دو مقدار یک دارند. به این ترتیب در مواقعی یک است، ایجاد جهش می کند.

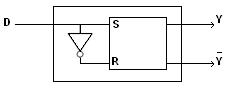

فلیپ فلاپ D

|

|

|

این مدار تاخیر دهنده شبیه به یک عنصر تاخیر دهنده ساعت عمل می کند به این ترتیب که هر ورودی به آن می دهیم در یک فاصله زمانی مشخصی بعدا همان ورودی را به صورت خروجی دریافت می کنیم.

از این رو این فلیپ فلاپ را فلیپ فلاپ تاخیر (Delay) می نامند. این فلیپ فلاپ یک ورودی به نام D دارد.

پیوندهای خارجی

- http://en.wikipedia.org/wiki/Flip-flop_%28electronics%29

- http://www.eelab.usyd.edu.au/digital_tutorial/part3/fl-types.htm

- http://hyperphysics.phy-astr.gsu.edu/hbase/electronic/flipflop.html#c1

- http://computer.howstuffworks.com/boolean3.htm

- http://www-ihs.theoinf.tu-ilmenau.de/~sane/projekte/flipflop/embed_flipflop.html

برچسبها: حسین ملکی, پیام نور شیراز, مهندسی برق پیام نور شیراز, مهندسی پیام نور شیراز

دسته بندی : قطعات الکترونیکی

موضوعات

- اخبار/فعالیت های انجمن علمی برق

- علمی

- اخبار تکنولوژی

- کار عملی

- قطعات الکترونیکی

- دانلود

- ابزار آلات مهندسی برق

- نمونه سوال/ پیام نور/آزاد/غیر انتفاعی/دولتی/

- نرم افزار های مهندسی برق

- فرهنگی/حدیث/طنز/حجاب

- PLC

- آموزش گام به گام میکروکنترلر

- جمع آوری پروژه های میکروکنترلری

- مدارهای کاربردی آنالوگ

- کتب و جزوات مهندسی برق

- مجلات تخصصی و مقالات

- آموزش پروتئوس

- معرفی شرکت های صنعت برق و الکترونیک

- منابع تغذیه ،شارژرها و باطری ها

- نمونه برنامه ها میکرو به زبان c و درایور ها

- آموزش برنامه نویسی

- میکرو و معرفی پروگرامر های خوب/PIC/AVR/ARM/DSPIC/

- معرفی برد های آموزشی داخلی و خارجی

- فعالیت باحال برقی

آرشیو مطالب

نویسندگان

درباره ما

بسیجی گمنام خمینی ٍ "" و لا یحمل هذا العلم الا اهل البصر و صبر و العلم به مواضع حق ""

و این پرچم مبارزه را جز افراد با بصیرت و صبور و آگاه به جایگاه حق به دوش نمی کشند .

این وبلاگ متعلق به گروهی از سربازان حقیقی حضرت بقیه الله الاعظم می باشد که در عرصه جهاد علمی و فرهنگی فعالیت می کند .

ایمیل : malekipcb@gmail.com

نویسنده: بسیجی گمنام خمینی

نویسنده: بسیجی گمنام خمینی  سه شنبه دهم اردیبهشت ۱۳۹۲ - 12:32

سه شنبه دهم اردیبهشت ۱۳۹۲ - 12:32